Progress #2

Posted on 2007/10/22 - 23:44Still no talk about the how, this 'week off' translated to close to 40 hours of work in just 4 days. So I was feeling like a trainwreck. The good news is that I put that much work in those few days because I was off for a little family holiday the rest of the week, which is also why this post is somewhat later. I'll try to do some things this week but I don't think much will happen due to other priorities I've got right now, like finishing some assignments for other classes and preparing for some tests that are coming up.

The schematic ended up getting a few final touches. Somebody mentioned that grounding all the remaining IO pins of the CPLD was a bad idea since an incorrect configuration could damange the CPLD this way. Better was to leave them unconnected and tie them high internally. I also dropped the second clock of 25.175Mhz. Although it seems important, I'm simply going to derive that (or at least 25MHz, which will also work without problems) from the 50MHz clock. Plus that IC was big and sitting in the way. Then, other voltages besides 3.3V were really appreciated on the extension connector, so I added all the power lines to it. Including -12V, which was a request and can be very handy for screens which need a contrast voltage. Finally I added a whole load of extra decoupling capacitors, found some properly sized electrolytic capacitors and added those, and changed all the packages of the resistors and capacitors to 0603. 0805 was non-stock for certain values I needed and so I had to use 0603 for some of them anyway.

So yeah, Thursday I made a final Bill of materials and ordered everything at Digikey. Turns out the spartan 3 FPGA I want is now backordered. Damnit! There is a smaller (200k instead of 400k gates) one available but I wouldn't save that much so that would be a bad idea. So in the end I just ordered it and it'll be delivered somewhere in December. Not that much of a problem since most of the development can and will be done in a simulator first but it's annoying nonetheless. Everything else got delivered two days later! Brilliant! Turns out that 0603 for a size is really small. Note the tiny black dot on the white paper. That's a resistor.

Oh sh..!

Digikey order & parts list in detail

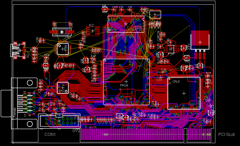

The rest of the week was spend completely on drawing the PCB which is, after pushing like crazy, still not finished. I'll hope to get to that point this week. I'm not going to release the brd file yet since I just know there are areas where wires get definately closer to eachother than 10 mil which will really end up incorrect. Also there are lots of power lines drawn as 10 mil lines, which is not going to work either. And the entire USB and JTAG area isn't drawn yet. Or drilling holes for a PCI bracket. Or the ground planes. And I haven't checked the solder mask and silk screen yet. Some art needs to be added, etc etc. There's still loads to do and I'm on it but I simply don't know when I'll have the time for it. I'm fairly sure it's not going to be this week.

Unfinished! Mayhem!

It would've helped a lot if I placed all components a little higher on the board, but I was stupid enough to draw the SDRAM connection first and with that it was pretty much impossible to move the FPGA anymore. Unless I was going to draw it all over again, which I really didn't feel like. So yes, the board is pretty cramped. Anyhow, that's about it. I promise that next time will be about how everything communicates. Later!

[: wacco :]

You're on the Project VGA Page

You're on the Project VGA Page